V tomto článku si projdeme multiplexer, nejprve definujeme, co je to multiplexer, poté projdeme jeho typy, které jsou 2×1 a 4×1, poté projdeme implementací muxu 2×1 a vyšší. mux s muxem nižšího řádu, Nakonec náš článek uzavřeme některými aplikacemi, výhodami a některými často kladenými dotazy.

Obsah

- Co jsou multiplexory?

- Typy muxů

- 2×1 multiplexer

- Multiplexer 4×1

- Implementace různých bran s 2:1 Mux

- Implementace MUX vyššího řádu pomocí MUX nižšího řádu

- Výhody a nevýhody MUX

Co jsou multiplexory?

Multiplexer je a kombinační obvod který má mnoho datových vstupů a jeden výstup v závislosti na ovládání nebo vybraných vstupech. Pro N vstupních řádků jsou vyžadovány log2(N) výběrové řádky nebo ekvivalentně pro

Multiplexer

Typy muxů

Mux může být různých typů na základě vstupu, ale v tomto článku si projdeme dva hlavní typy muxů, které jsou

- 2×1 Mux

- 4×1 Mux

2×1 multiplexer

2×1 je základní obvod, který je také známý jako 2-to-1 multiplexer, který se používá k výběru jednoho signál ze dvou vstupů a přenáší jej na výstup. Mux 2×1 má dvě vstupní linky, jednu výstupní linku a jednu výběrovou linku. Má různé aplikace v digitálních systémech, jako je mikroprocesor, používá se k výběru mezi dvěma různými zdroji dat nebo mezi dvěma různými instrukcemi.

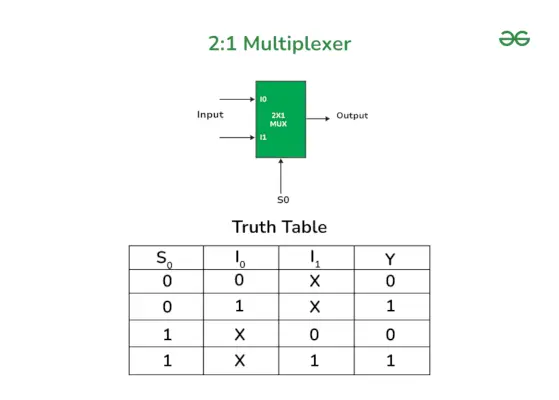

Blokové schéma multiplexeru 2:1 s tabulkou pravdy

Níže je uveden blokový diagram a pravdivostní tabulka 2:1 Mux. V tomto blokovém diagramu, kde I0 a I1 jsou vstupní linky, Y je výstupní linka a S0 je jedna volicí linka.

Blokové schéma multiplexeru 2:1 s tabulkou pravdy

Výstup 2×1 Mux bude záviset na řádku výběru S0,

- Když je S 0 (nízká), zvolí se I0

- když je S0 1 (Vysoká), zvolí se I1

Logické vyjádření 2×1 Mux

Pomocí tabulky pravdy lze určit logický výraz pro Mux jako

Y=overline{S_0}.I_0+S_0.I_1

Schéma zapojení 2×1 multiplexerů

Pomocí pravdivostní tabulky obvod diagram může být uveden jako

Schéma zapojení 2×1 Mux

Multiplexer 4×1

Multiplexer 4×1, který je také známý jako multiplexor 4 na 1. Jedná se o multiplexer, který má 4 vstupy a jeden výstup. Výstup je vybrán jako jeden ze 4 vstupů, který je založen na výběrových vstupech. Počet řádků výběru bude záviset na počtu vstupu, který je určen rovnicí

Blokové schéma multiplexeru 4×1

V daném blokovém diagramu jsou I0, I1, I2 a I3 4 vstupy a Y je samostatný výstup, který je založen na výběrových liniích S0 a S1.

Výstup multiplexeru je určen binární hodnotou výběrových řádků

- Když S1S0=00, je zvolen vstup I0.

- Když S1S0=01, je zvolen vstup I1.

- Když S1S0=10, je zvolen vstup I2.

- Když S1S0=11, je zvolen vstup I3.

Pravdivostní tabulka 4×1 multiplexeru

Níže je uvedeno Tabulka pravdy multiplexeru 4×1

to je

Schéma zapojení 4×1 multiplexerů

Pomocí pravdivostní tabulky lze schéma zapojení zadat jako

Multiplexor může fungovat jako univerzální kombinační obvod. Všechna standardní logická hradla lze implementovat pomocí multiplexerů.

Implementace různých bran s 2:1 Mux

Níže je uvedena implementace různé brány pomocí 2:1 Mux

faktoriál v c

Implementace brány NOT pomocí 2 : 1 Mux

Bránu Not z 2:1 Mux lze získat pomocí

- Připojte vstupní signál k jednomu ze vstupních datových linek (I0).

- Poté připojte vedení (0 nebo 1) k druhému vstupnímu datovému vedení (I1)

- Připojte stejnou vstupní linku Vyberte linku S0, která je připojena k D0.

Níže je uveden diagram pro logickou reprezentaci NE brána pomocí 2:1 Mux

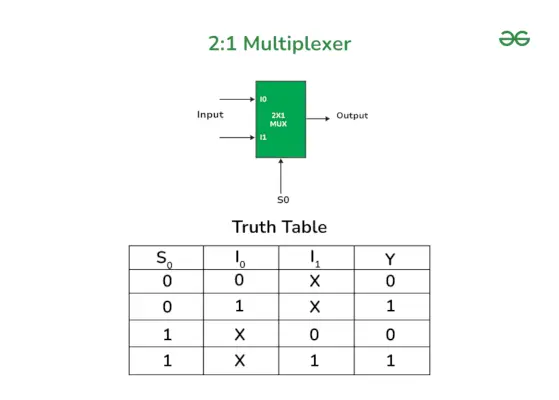

Implementace AND hradla pomocí 2 : 1 Mux

Bránu And z 2:1 Mux lze získat pomocí

- Připojte vstup Y k I1.

- Připojte vstup X k výběrovému řádku S0.

- Připojte vedení (0) k I0.

Níže je uveden diagram pro logickou reprezentaci A brána pomocí 2:1 Mux

Pro další více na Implementace AND hradla pomocí 2 : 1 Mux

Realizace OR brány pomocí 2 : 1 Mux

Bránu OR z 2:1 Mux lze získat pomocí

- Připojte vstup X k výběrovému řádku S0.

- Připojte vstup Y k I1.

- Připojte vedení (1) k I1.

Níže je uveden diagram pro logickou reprezentaci NEBO brána pomocí 2:1 Mux

Implementace hradel NAND, NOR, XOR a XNOR vyžaduje dva 2:1 Mux. První multiplexor bude fungovat jako brána NOT, která bude poskytovat doplňkový vstup pro druhý multiplexor.

Implementace hradla NAND pomocí 2 : 1 Mux

Bránu NAND z 2:1 Mux lze získat o

- V prvním muxu vezměte vstupy a 1 a 0 a y jako řádek výběru.

- V druhém MUX je výstup z muxu připojen k I1.

- řádek(1) je dán I0.

- x je uvedeno jako výběrový řádek pro druhý Mux.

Níže je uveden diagram pro logickou reprezentaci Brána NAND pomocí 2:1 Mux

Pro další více na Implementace hradla NAND pomocí 2 : 1 Mux

Implementace brány NOR pomocí 2 : 1 Mux

Bránu Nor z 2:1 Mux lze získat pomocí

- V prvním muxu vezměte vstupy a 1 a 0 a y jako řádek výběru.

- V druhém MUX je výstup z muxu připojen k I0.

- řádek (0) je dán I1.

- x je uvedeno jako výběrový řádek pro druhý Mux.

Níže je uveden diagram pro logickou reprezentaci NOR brána pomocí 2:1 Mux

Pro další více na Realizace hradla NOR pomocí 2 : 1 Mux

Realizace hradla EX-OR pomocí 2 : 1 Mux

Bránu Nor z 2:1 Mux lze získat pomocí

- V prvním muxu vezměte vstupy a 1 a 0 a y jako řádek výběru.

- V druhém MUX je výstup z muxu připojen k I1.

- y je dáno I0.

- x je uvedeno jako výběrový řádek pro druhý Mux.

Níže je uveden diagram pro logickou reprezentaci EX-OR brána pomocí 2:1 Mux

Implementace hradla EX-NOR pomocí 2 : 1 Mux

Níže je uveden diagram pro logickou reprezentaci EX-OR brána pomocí 2:1 Mux

Bránu Nor z 2:1 Mux lze získat pomocí

- V prvním muxu vezměte vstupy a 1 a 0 a y jako řádek výběru.

- V druhém MUX je výstup z muxu připojen k I0.

- y je dáno I1.

- x je uvedeno jako výběrový řádek pro druhý Mux.

Implementace MUX vyššího řádu pomocí MUX nižšího řádu

Níže je uvedena implementace MUX vyššího řádu pomocí MUX nižšího řádu

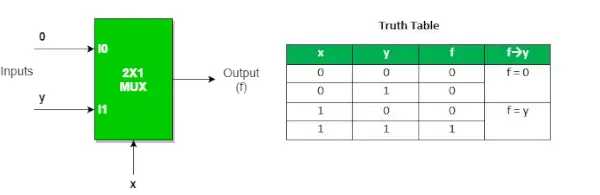

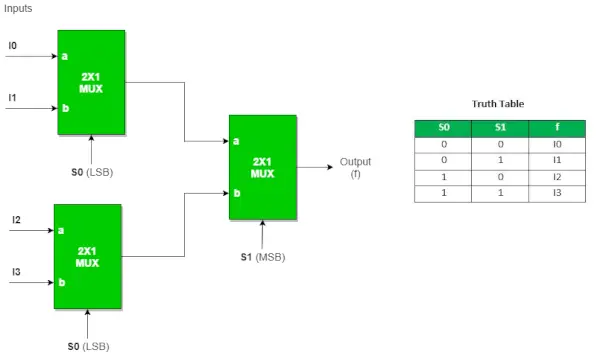

4 : 1 MUX pomocí 2 : 1 MUX

K implementaci 4:1 MUX jsou zapotřebí tři 2:1 MUX.

Podobně,

Zatímco 8:1 MUX vyžaduje sedm (7) 2:1 MUX, 16:1 MUX vyžaduje patnáct (15) 2:1 MUX a 64:1 MUX vyžaduje šedesát tři (63) 2:1 MUX. Můžeme tedy vyvodit závěr, že an

16 : 1 MUX pomocí 4 : 1 MUX

Níže je uveden logický diagram 16:1 Mux pomocí 4:1 Mux

Obecně platí, že pro implementaci B : 1 MUX pomocí A : 1 MUX se k implementaci téhož používá jeden vzorec.

B/A = K1,

K1/ A = K2,

K2/A = K3

KN-1/ A = KN= 1 (dokud nezískáme 1 počet MUX).

A pak sečtěte všechna čísla MUXů = K1 + K2 + K3 + …. + KN.

Pro implementaci 64 : 1 MUX pomocí 4 : 1 MUX

Pomocí výše uvedeného vzorce můžeme získat totéž.

64/4 = 16

16/4 = 4

4 / 4 = 1 (dokud nezískáme 1 počet MUX)

K implementaci 64 : 1 MUX = 16 + 4 + 1 = 21 je tedy zapotřebí celkový počet 4 : 1 MUX.

f (A, B, C) =

pomocí A a B jako výběrových linek pro 4 : 1 MUX,

AB jako výběr: Rozbalíte-li minterms na booleovskou formu a uvidíte jejich hodnotu 0 nebo 1 na C-tém místě, takže je lze umístit tímto způsobem.

AC jako výběr : Rozbalí se minterms na jeho booleovskou formu a na B-tém místě se zobrazí jejich hodnota 0 nebo 1, takže je lze umístit tímto způsobem.

BC jako výběr : Rozšíření minterms na jeho booleovskou formu a v A uvidí jeho hodnotu 0 nebo 1čtumístit tak, aby mohly být umístěny tímto způsobem.

porovnání řetězců v Javě

Výhody a nevýhody MUX

Níže jsou uvedeny výhody a nevýhody MUX

Výhody MUXu

Níže jsou uvedeny výhody MUX

- Účinnost : Mux má dobrou účinnost při směrování více vstupních signálů do jediného výstupního signálu na základě řídicích signálů.

- Optimalizace : Mux pomáhá šetřit zdroje, jako jsou dráty, kolíky a integrovaný obvod (IC).

- Různé implementace: Mux lze použít k implementaci různých digitálních logických funkcí, jako je AND, OR atd.

- Flexibilita: Mux lze snadno konfigurovat podle požadavků a přizpůsobit se různým zdrojům dat, což zvyšuje všestrannost systému.

Nevýhody MUX

Níže jsou uvedeny nevýhody MUX

- Omezený počet zdrojů dat: Počet vstupů, které může mít multiplexor, je omezen počtem řídicích linek, což může způsobit omezení v určitých aplikacích.

- Zpoždění: Multiplexory mohou mít určité zpoždění v signálové cestě, což může mít dopad na výkon obvodu.

- Zdůvodnění komplexního ovládání: Logika řízení pro multiplexory může být složitá, zejména pro větší multiplexory s velkým počtem vstupů.

- Spotřeba energie: Multiplexory mohou spotřebovat více energie ve srovnání s jinými jednoduchými l ogická brána , zvláště když mají velký počet vstupů.

Aplikace MUX

Níže jsou uvedeny aplikace MUX

- Směrování dat : Mux se používá pro směrování dat v digitálním systému, kde vyberou jednu z několika datových linek a přesměrují ji na výstup.

- Výběr dat : Mux se používá pro výběr dat, kde volí zdroj dat podle výběrových řádků.

- Převod analogového signálu na digitální : Mux se používají v ADC pro výběr různých analogových vstupních kanálů.

- Dekódování adresy : Mux se používají v Mikroprocesory nebo paměť pro dekódování adresy.

- Implementace logické funkce : Muxy lze použít k implementaci různých logických funkcí.

Závěr

V tomto článku jsme prošli MUX, viděli jsme různé typy muxů, které jsou 2×1 a 4×1 mux, prošli jsme implementací muxu 2×1 a vyššího muxu s muxem nižšího řádu. Také jsme ve stručnosti prošli jeho výhody, nevýhody a aplikace.

Multiplexery v digitální logice – FAQ

Proč je řídicí logika pro multiplexery považována za složitou?

Mux může být složitý zejména pro větší multiplexery kvůli řídicím signálům, které vybírají vstupy na základě požadavků aplikace.

Jaké jsou různé typy architektur multiplexerů?

Architektury muxů se mění na základě faktorů, jako je celkový počet vstupů, počet vybraných linek a logika použitá pro výběr vstupu.

Jak se používají multiplexory aplikace digitálního zpracování signálu (DSP)?

V aplikacích DSP se multiplexory používají pro směrování, výběr a zpracování signálu.