A Čelit je zařízení, které ukládá (a někdy zobrazuje) počet případů, kdy k určité události nebo procesu došlo, často ve vztahu k hodinovému signálu. Čítače se používají v digitální elektronice pro účely počítání, mohou počítat konkrétní událost, která se děje v obvodu. Například v UP counter čítač zvyšuje počet pro každou vzestupnou hranu hodin. Nejen počítání, počítadlo může sledovat určitou sekvenci založenou na našem návrhu jako jakákoli náhodná sekvence 0,1,3,2… . Mohou být také navrženy pomocí klopných obvodů. Používají se jako frekvenční děliče, kde se dělí frekvence daného pulzního průběhu. Čítače jsou sekvenční obvody, které počítají počet impulsů, mohou být buď v binárním kódu nebo ve formě BCD. Hlavní vlastnosti čítače jsou časování , sekvenování a počítání. Čítač pracuje ve dvou režimech

Nahoře pult

Spodní pult

Protiklasifikace

Počítadla jsou obecně rozdělena do dvou kategorií

- Asynchronní čítač

- Synchronní čítač

1. Asynchronní čítač

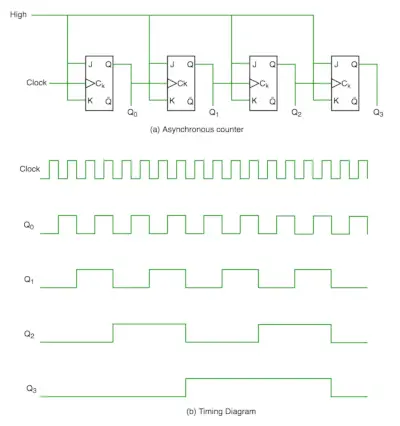

V asynchronním čítači nepoužíváme univerzální hodiny, pouze první klopný obvod je řízen hlavními hodinami a hodinový vstup zbytku následujícího klopného obvodu je řízen výstupem předchozích klopných obvodů. Můžeme to pochopit z následujícího diagramu -

Z časového diagramu je zřejmé, že Q0 se mění, jakmile je zaznamenána náběžná hrana hodinového impulsu, Q1 se mění, když je zaznamenána náběžná hrana Q0 (protože Q0 je jako hodinový impuls pro druhý klopný obvod) a tak dále. Tímto způsobem jsou generovány vlnky prostřednictvím Q0, Q1, Q2, Q3, proto se také nazývá Čítač RIPPLE a sériové počítadlo. Čítač zvlnění je kaskádové uspořádání klopných obvodů, kde výstup jednoho klopného obvodu řídí hodinový vstup následujícího klopného obvodu.

2. Synchronní čítač

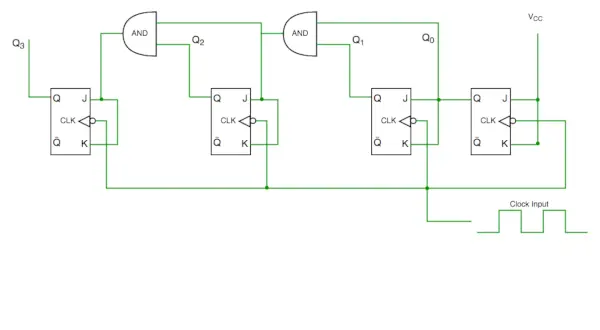

Na rozdíl od asynchronního čítače má synchronní čítač jedny globální hodiny, které řídí každý klopný obvod, takže se výstup mění paralelně. Jednou z výhod synchronního čítače oproti asynchronnímu je, že může pracovat na vyšší frekvenci než asynchronní čítač, protože nemá kumulativní zpoždění, protože každý klopný obvod má stejné hodiny. Nazývá se také jako paralelní čítač.

Synchronní čítačový obvod

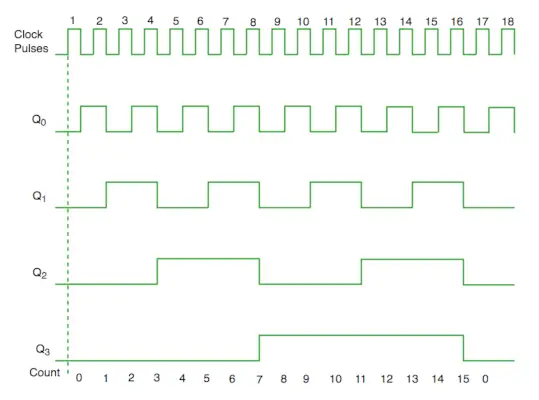

Časový diagram synchronní čítač

Ze schématu zapojení vidíme, že bit Q0 dává odezvu na každou sestupnou hranu hodin, zatímco Q1 je závislý na Q0, Q2 je závislý na Q1 a Q0, Q3 je závislý na Q2, Q1 a Q0.

Počítadlo desetiletí

Počítadlo dekády počítá deset různých stavů a poté se resetuje do výchozích stavů. Jednoduchý čítač dekády bude počítat od 0 do 9, ale můžeme také vytvořit čítače dekády, které mohou procházet libovolnými deseti stavy mezi 0 až 15 (pro 4bitové počítadlo).

| Hodinový puls | Q3 | Q2 | Q1 | Q0 |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 |

| 10 | 0 | 0 | 0 | 0 |

Tabulka pravdy pro jednoduché počítadlo desetiletí

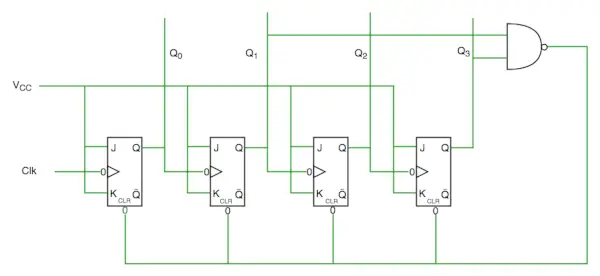

Schéma zapojení čítače dekády

Ze schématu zapojení vidíme, že jsme použili nand hradlo pro Q3 a Q1 a přivedli to k vymazání vstupní linky, protože binární reprezentace 10 je —

1010

A vidíme, že Q3 a Q1 jsou zde 1, pokud dáme NAND těchto dvou bitů k vymazání vstupu, pak se čítač vymaže na 10 a začne znovu od začátku.

Důležitý bod : Počet klopných obvodů použitých v počítadle je vždy větší než roven ( log2n ) kde n=počet stavů v čítači.

Některé otázky brány z minulých let na přepážkách

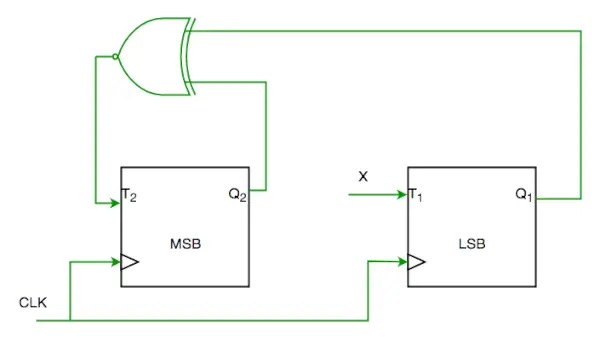

Q1. Zvažte částečnou implementaci 2bitového čítače pomocí T klopných obvodů podle sekvence 0-2-3-1-0, jak je uvedeno níže

Pro dokončení obvodu by měl být vstup X

(A) Q2?

(B) Q2 + Q1

(C) (Q1 ? Q2)'

(D) Q1? Q2 (GATE-CS-2004)

Řešení:

Z okruhu vidíme

T1=XQ1'+X'Q1—-(1)

A

T2=(Q2 ? Q1)'—-(2)

A POŽADOVANÝ VÝSTUP JE 00->10->11->01->00

TAK BY MĚLO BÝT X Q1Q2’+Q1’Q2 SPOKOJENÉ 1 A 2.

TAKŽE ANS JE (D) ČÁST.

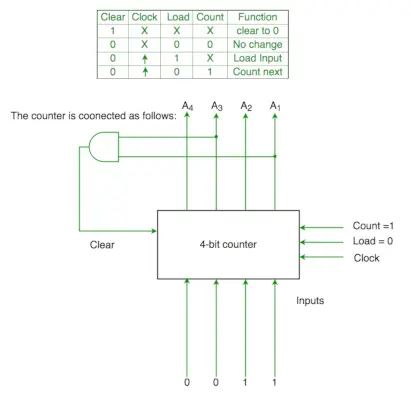

Q2. Funkce řídicího signálu 4bitového binárního čítače jsou uvedeny níže (kde X je jedno)

Čítač je připojen následovně:

Předpokládejme, že zpoždění čítače a brány je zanedbatelné. Pokud čítač začíná na 0, pak cyklicky prochází následující sekvencí:

(A) 0,3,4

(B) 0,3,4,5

(C) 0,1,2,3,4

(D) 0,1,2,3,4,5 (GATE-CS-2007)

Řešení:

Zpočátku A1 A2 A3 A4 =0000

Clr = AI a A3

Takže když jsou A1 a A3 oba 1, jde znovu na 0000

Proto 0000(init.) -> 0001(A1 a A3=0)->0010 (A1 a A3=0) -> 0011(A1 a A3=0) -> 0100 ( A1 a A3=1 )[ jasná podmínka splněna] ->0000(init.), takže to projde 0->1->2->3->4

Ans je část (C).

zkrátit a odstranit rozdíl

Kvíz o digitální logice

Článek přispěl Anuj Batham,