Flip-flop je termín, který spadá pod digitální elektroniku a je to elektronická součástka, která se používá k uložení jednoho bitu informace.

Schématické znázornění Flip Flopu

- Protože Flip Flop je sekvenční obvod, jeho vstup je založen na dvou parametrech, jeden je aktuální vstup a druhý je výstup z předchozího stavu.

- Má dva výstupy, oba se vzájemně doplňují.

- Může být v jednom ze dvou stabilních stavů, buď 0 nebo 1.

Základní schéma Flip Flop

Co je T Flip Flop?

- T flip flop nebo přesněji je známý jako Toggle Flip Flop, protože dokáže přepínat svůj výstup v závislosti na vstupu.

- T zde znamená Přepnout .

- Toggle v podstatě znamená, že bit bude překlopen, tj. buď z 1 na 0, nebo z 0 na 1.

- Zde je k ovládání tohoto flopu přiváděn hodinový impuls, jedná se tedy o taktovaný klopný obvod.

Konstrukce T Flip Flop

T flip můžeme konstruovat třemi způsoby:

- Pomocí SR Flip Flops.

- Pomocí D Flip Flops.

- Pomocí JK Flip Flops

Způsoby konstrukce T Flip Flop

Podívejme se na konstrukci T Flip Flop pomocí SR Flip Flops, které vyžadují 2 hradla AND a 2 hradla NOR, jak je znázorněno níže:

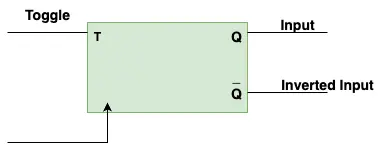

Základní blokové schéma T Flip Flop

Zde blokové schéma obsahuje Toggle a hodinové vstupy, Q a Q' jsou doplněné vstupy.

Práce s T Flip Flop

Případ 1 : Řekněme, T = 0 a hodinový puls je vysoký tj. 1, pak bude výstup obou hradla AND 1 a hradla AND 2 0 , brána 3 výstup bude Q a podobně brána 4 výstup bude Q' takže obě hodnoty Q a Q' jsou stejné jako jejich předchozí hodnota, což znamená Držte stav .

Případ 2 : Řekněme, T=1 , pak bude výstup obou hradel AND 1 (T * hodiny * Q) , a protože T a hodiny jsou oba 1, pak výstup AND hradla 1 bude Q , a podobně bude výstup AND hradla 2 (T * hodiny * Q') tj., Q' . Nyní bude výstup brány 3 (Q'+Q)' a řekněme, že Q' je nula, pak bude výstup brány 3 (0+Q)“ což znamená Q' a podobně bude výstup brány 4 (Q+Q')' a protože Q' je nula, takže výstup brány 4 bude Q', což znamená 0 protože Q' je nula. V tomto případě tedy můžeme říci, že výstup se přepíná, protože T=1 .

Pravdivostní tabulka T Flip Flop

- Zde je T přepínací vstup, Q je vstup aktuálního stavu, Qt+1 je výstup dalšího stavu.

- Odtud můžeme vidět, že kdykoli je Toggle (T) 0, výstup dalšího stavu (Qt+1) je stejný jako vstup aktuálního stavu (Q).

- Kdykoli je Toggle (T) 1, výstup dalšího stavu (Qt+1) bude doplňkem vstupu aktuálního stavu (Q), což znamená, že se přepne.

Charakteristická rovnice

- Charakteristická rovnice nám říká, jaký bude další stav klopného obvodu z hlediska současného stavu.

- Aby bylo možné získat charakteristickou rovnici, je vytvořena mapa K, která bude zobrazena níže:

- Pokud vyřešíme výše uvedenou K-mapu, pak bude charakteristická rovnice Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabulka buzení

Tabulka buzení v podstatě vypovídá o buzení, které klopný obvod vyžaduje pro přechod z aktuálního stavu do dalšího stavu.

- Zde platí, že kdykoli je T 0, Qt+1 je stejné jako vstup Q.

- A kdykoli je T 1, Qt+1 je kompliment vstupu Q.

Aplikace T Flip Flop

Existuje mnoho aplikací T Flip Flop v digitálním systému, které jsou uvedeny níže:

- Počítadla : T Flip Flops používané v pultech. Čítače počítají počet událostí, které nastanou v digitálním systému.

- Datové úložiště : T Flip Flops slouží k vytvoření paměti, která se používá k ukládání dat, když je napájení vypnuto.

- Synchronní logické obvody : T klopné obvody lze použít k implementaci synchronních logických obvodů, což jsou obvody, které provádějí operace s binárními daty na základě hodinového signálu. Synchronizací operací logického obvodu s hodinovým signálem pomocí T klopných obvodů lze chování obvodu učinit předvídatelným a spolehlivým.

- Frekvenční dělení : Používá se k dělení frekvence hodinového signálu 2. Flip-flop přepne svůj výstup pokaždé, když hodinový signál přejde z vysoké na nízkou nebo z nízké na vysokou, proto se hodinová frekvence vydělí 2.

- Posunové registry : T klopné obvody lze použít v posuvných registrech, které se používají k posunu binárních dat jedním směrem.

Závěr

V tomto článku začínáme od základů klopných obvodů, tedy co to vlastně jsou klopné obvody, a poté jsme diskutovali o klopných obvodech T, třech dvou způsobech, kterými můžeme konstruovat klopné obvody T, je to základní blokový diagram, fungování klopných obvodů T , je to tabulka pravdy, charakteristická rovnice a také tabulka buzení a na závěr jsme diskutovali o aplikacích T klopných obvodů.